近日,杭州电子科技大学芯片与安全实验室(CSL)博士生胡子腾在导师夏莹杰教授指导下,与浙江大学、中南大学和华中科技大学科研团队合作完成的芯片安全设计研究成果“SecFSM: Knowledge Graph-Guided LLMs for Generating Secure Verilog Code of Finite State Machine in SoCs”被IEEE Transactions on Dependable and Secure Computing(CCF-A、TOP期刊,IF=7.5)发表。实验室博士生胡子腾为论文第一作者,夏莹杰教授为通讯作者。

有限状态机(FSM)通常使用Verilog实现,是系统级芯片(SoC)控制逻辑的基础。随着近年来用于代码生成的大语言模型(LLM)的进展,LLM在Verilog代码生成方面的应用日益受到关注。然而,LLM生成的Verilog代码频繁出现安全漏洞,这对于安全关键型FSM设计而言尤为棘手。

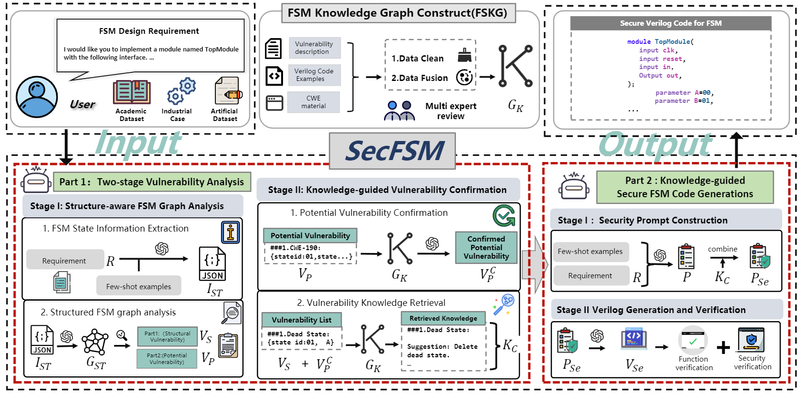

图1 SecFSM总体流程图

本文提出SecFSM方法,利用面向安全的知识图谱引导LLM生成更安全的Verilog代码。具体而言,首先构建了FSM安全知识图谱(FSKG),这是一个面向FSM的多层知识模式,在三个层面(即FSM漏洞、漏洞语义、缓解措施与安全设计模式)组织安全知识。然后,根据由自然语言需求构成的用户输入,我们构建了具有显式安全语义的结构化FSM图。在此模型基础上,设计了两阶段漏洞分析算法:(i)结构化FSM图分析,用于识别结构性与潜在漏洞;(ii)通过FSKG上的语义推理进行知识引导的漏洞确认。最终,将这种与FSKG显式对齐的结构化漏洞知识,融入面向FSM结构感知的三阶段安全提示模板,以指导受安全约束的Verilog FSM生成。

IEEE Transactions on Dependable and Secure Computing作为中国计算机学会(CCF)推荐的信息安全领域三本A类期刊之一,影响因子为7.5,是国际公认的顶级期刊。

杭州电子科技大学CSL实验室,成员涵盖本、硕、博各阶段学生,形成了独具特色的人才培养模式。实验室聚焦物联网安全、芯片安全等国家亟需领域,为每位学生制定面向国际前沿的研究规划,并与清华大学、浙江大学、中南大学等高校建立联合培养模式,优秀学生长期与这些高校研究团队开展紧密合作与交流访学,力争产出具有国际影响力的一流成果。欢迎志向高远、具有自驱力的优秀学生加入CSL实验室!